- 您现在的位置:买卖IC网 > Sheet目录1994 > DS3105LN+ (Maxim Integrated Products)IC TIMING LINE CARD 64-LQFP

DS3105

100

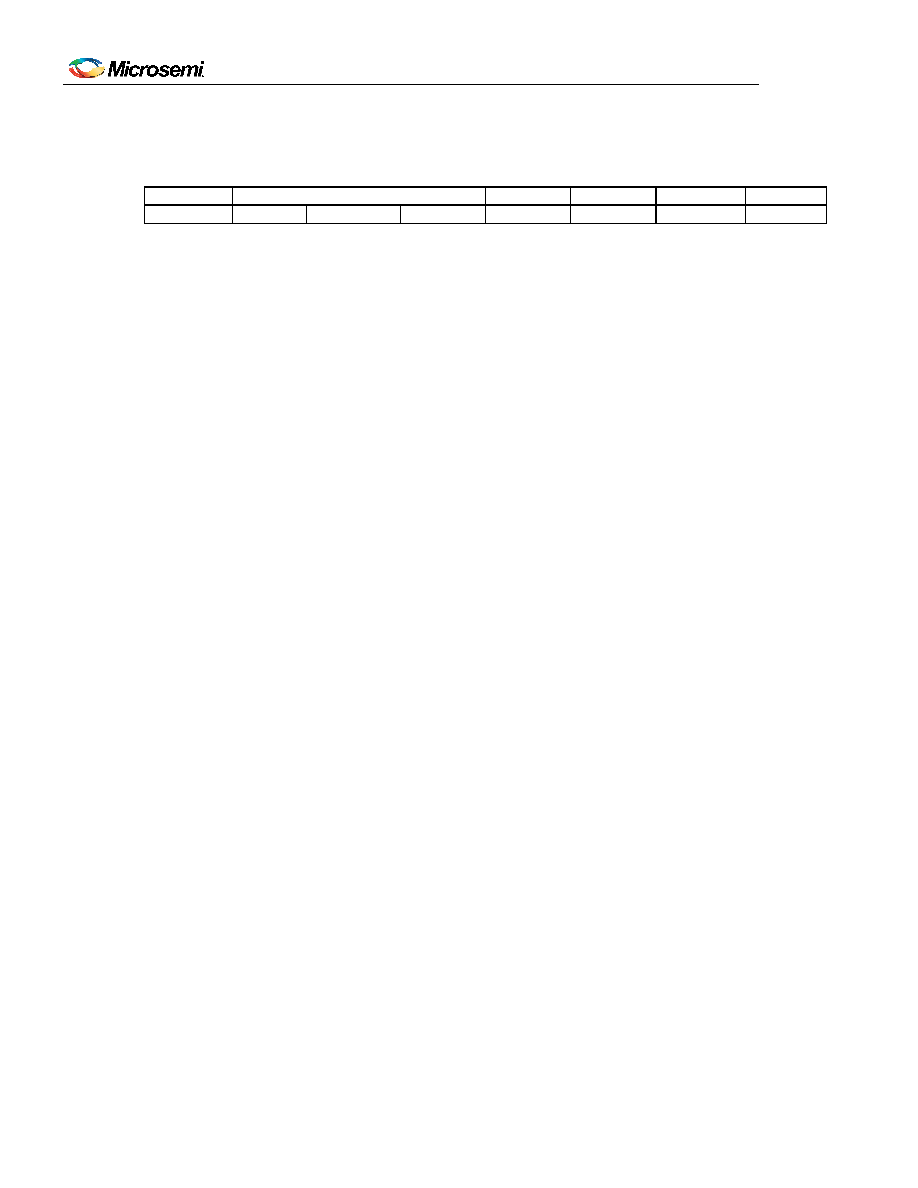

Register Name:

FSCR1

Register Description:

Frame-Sync Configuration Register 1

Register Address:

7Ah

Bit #

7

6

5

4

3

2

1

0

Name

—

SYNCSRC[2:0]

8KINV

8KPUL

2KINV

2KPUL

Default

0

Bits 6 to 4: SYNC12 Source (SYNCSRC[2:0]). When external frame sync is configured for SYNC123 mode, this

field specifies the input clocks to associate with the SYNC1 and SYNC2 pins. SYNC3 is always associated with

input clock IC9 in this mode. See Section 7.9.1.

0XX = SYNC1 pin associated with IC3 or IC5, SYNC2 pin associated with IC4 or IC6

1X0 = SYNC1 pin associated with IC3, SYNC2 pin associated with IC4

1X1 = SYNC1 pin associated with IC5, SYNC2 pin associated with IC6

Bit 3: 8kHz Invert (8KINV). When this bit is set to 1 the 8kHz signal on clock output FSYNC is inverted. See

Section 7.8.2.5.

0 = FSYNC not inverted

1 = FSYNC inverted

Bit 2: 8kHz Pulse (8KPUL). When this bit is set to 1, the 8kHz signal on clock output FSYNC is pulsed rather than

50% duty cycle. In this mode output clock OC3 must be enabled, and the pulse width of FSYNC is equal to the

clock period of OC3. See Section 7.8.2.5.

0 = FSYNC not pulsed; 50% duty cycle

1 = FSYNC pulsed, with pulse width equal to OC3 period

Bit 1: 2kHz Invert (2KINV). When this bit is set to 1 the 2kHz signal on clock output MFSYNC is inverted. See

Section 7.8.2.5.

0 = MFSYNC not inverted

1 = MFSYNC inverted

Bit 0: 2kHz Pulse (2KPUL). When this bit is set to 1, the 2kHz signal on clock output MFSYNC is pulsed rather

than 50% duty cycle. In this mode output clock OC3 must be enabled, and the pulse width of MFSYNC is equal to

the clock period of OC3. See Section 7.8.2.5.

0 = MFSYNC not pulsed; 50% duty cycle

1 = MFSYNC pulsed, with pulse width equal to OC3 period

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS3106LN+

IC TIMING LINE CARD 64-LQFP

DS3231MZ+

IC RTC I2C 8SOIC

DS3231SN#T&R

IC RTC W/TCXO 16-SOIC

DS3232MZ+

IC RTC W/SRAM I2C 8SOIC

DS3232SN#T&R

IC RTC W/TCXO 20-SOIC

DS3234S#

IC RTC W/TCXO 20-SOIC

DS32C35-33#T&R

IC RTC ACCURATE I2C 3.3V 20-SOIC

DS3911T+

IC DAC 10BIT I2C QUAD 14TDFN

相关代理商/技术参数

DS3106

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Line Card Timing IC

DS3106A10SL3S(621)

制造商:Amphenol Corporation 功能描述:

DS3106A14S2S

制造商:Amphenol Corporation 功能描述:

DS3106A14S2S(621)

制造商:Amphenol Corporation 功能描述:

DS3106A14S5P

制造商:Amphenol Corporation 功能描述:

DS3106A14S5P(621)

制造商:Amphenol Corporation 功能描述:

DS3106A14S5S(621)

制造商:Amphenol Corporation 功能描述:

DS3106A14S6P

制造商:Amphenol Corporation 功能描述: